A、 改变时序控制方式

B、 改变微指令格式

C、 增加微命令个数

D、 改变控制存储器的内容

答案:D

解析:【答案解析】在微程序控制的计算机中,若要修改指令系统,只需修改相应指令的微程序即 可。这些微程序都存放在控制存储器中,所以只需改变控制存储器的内容。【归纳总结】微程序控制器的设计思想和组合逻辑控制器的设计思想截然不同。它具有设计 规整、调试、维修以及更改、扩充指令方便的优点,易于实现自动化设计,已成为当前控制器 的主流。但是,由于它增加了一级控制存储器,所以指令执行速度比组合逻辑控制器慢。

A、 改变时序控制方式

B、 改变微指令格式

C、 增加微命令个数

D、 改变控制存储器的内容

答案:D

解析:【答案解析】在微程序控制的计算机中,若要修改指令系统,只需修改相应指令的微程序即 可。这些微程序都存放在控制存储器中,所以只需改变控制存储器的内容。【归纳总结】微程序控制器的设计思想和组合逻辑控制器的设计思想截然不同。它具有设计 规整、调试、维修以及更改、扩充指令方便的优点,易于实现自动化设计,已成为当前控制器 的主流。但是,由于它增加了一级控制存储器,所以指令执行速度比组合逻辑控制器慢。

A. PCI、CRT、USB、EISA

B. ISA、CPI、VESA、EISA

C. ISA、SCSI、RAM、MIPS

D. ISA、EISA、PCI、PCI-Express

A. Ⅰ和Ⅱ

B. Ⅲ

C. Ⅳ

D. Ⅴ和Ⅵ

解析:【答案解析】采用进位位来判断溢出时,当最高有效位和符号位的值不相同时才会产生溢出。【归纳总结】两正数相加,当最高有效位产生进位(C1=1)而符号位不产生进位(Cs=0)时,发生 正溢;两负数相加,当最高有效位不产生进位(C1=0)而符号位产生进位(Cs=1)时,发生负溢。 故溢出条件为:溢出=CsC1+CsC1=Cs ⊕ C1。

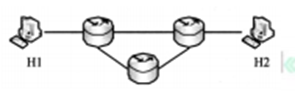

A. 10 Mbps

B. 20 Mbps

C. 80 Mbps

D. 100 Mbps

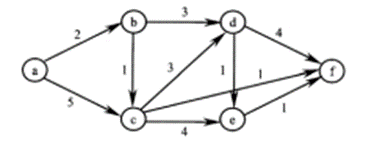

A. d,e,f

B. e,d,f

C. f,d,e

D. f,e,d

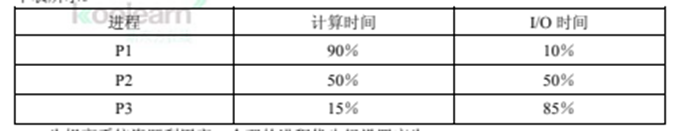

为提高系统资源利用率,合理的进程优先级设置应为

为提高系统资源利用率,合理的进程优先级设置应为

A. P1>P2>P3

B. P3>P2>P1

C. P2>P1=P3

D. P1>P2=P3

A. 80 ms

B. 80.08 ms

C. 80.16 ms

D. 80.24 ms

A. DIV R0,R1 ;(R0)/(R1)→R0

B. INT n ; 产生软中断

C. NOT R0 ;寄存器R0的内容取非

D. MOV R0,addr;把地址addr处的内存数据放入寄存器R0中

A. r1×r2

B. r2×r3

C. r1×r4

D. r2×r4

A. i-j-1

B. i-j

C. j-i+1

D. 不确定

解析:【答案解析】一串数据依次通过一个栈,并不能保证出栈数据的次序总是倒置,可以产生多 种出栈序列。一串数据通过一个栈后的次序由每个数据之间的进栈、出栈操作序列决定,只 有当所有数据“全部进栈后再全部出栈”才能使数据倒置。事实上,存在一种操作序列——“进栈、出栈、进栈、出栈……”——可以使数据通过栈后仍然保持次序不变。 题目中输出序列的第一个元素是 i,则第 j 个输出元素是不确定的。

A. S1 的栈底位置为 0,S2 的栈底位置为 n-1

B. S1 的栈底位置为 0,S2 的栈底位置为 n/2

C. S1 的栈底位置为 0,S2 的栈底位置为 n

D. S1 的栈底位置为 0,S2 的栈底位置为 1

解析:【答案解析】利用栈底位置不变的特性,可让两个顺序栈共享一个一维数据空间,以互补余 缺,实现方法是:将两个栈的栈底位置分别设在存储空间的两端,让它们的栈顶各自向中间 延伸。这样,两个栈的空间就可以相互调节,只有在整个存储空间被占满时才发生上溢,这 样一来产生上溢的概率要小得多。